E-ISSN: 2319-4200, P-ISSN: 2319-4197

Www.Iosrjournals.Org

# Design And Implementation Of 4×4 Vedic Multiplier With Reduced Transistor Count And Competitive Power Consumption

# Author

#### Abstract

The multiplication is one of the most important arithmetic function in Digital signal processing, ALU and various communication systems. The Multiplication method require more hardware resources and more time than other arithmetic and logical circuits such as Addition, Subtraction etc. But the need for fast computation along with low on chip area and the low power dissipation is increased in recent times. In recent years, lot of work has been done to improve speed of multiplier while reducing transistor count(on chip area). The different designs such as Array multiplier, Wallace-tree multiplier and Vedic multiplier are proposed. The Vedic multiplication is based on the ancient Indian literature called as sutras.

In this paper we have proposed architecture of 4×4 Vedic multiplier based on the Urdhva-Tiryagbhyam sutra along with some modifications in it. It uses the standard designed blocks such as AND gate, OR gate, Half Adder and the Full Adder blocks to implement the 4×2 vedic multiplier. Then with help of designed 4×4 vedic multiplier further 4×4 vedic multiplier is designed. This 4×4 multiplier is design and simulated in the cadence virtuoso software with the help of 180 nm technology. The results of proposed design show an improvement of approx 70% in the on chip area and 73% less delay in comparison to CMOS Vedic multiplier.

Key words:- Vedic Multiplier, 180 nm, Cadence Virtuoso, Transistor count.

Date of Submission: 19-04-2024 Date of Acceptance: 29-04-2024

# I. Introduction To Vedic Multiplication

Multiplication is a mathematical operation. The Number repeatedly added to itself for the specific number of times. For example if A multiplied by B, then A is added B times with itself Multipliers required more on chip area and propagation time, than other arithmetic operations. Processors spend enormous amounts of time and a lot of hardware on multiplying, in order to make the multiplication as fast as possible [1].So, considering this the design of hybrid vedic multiplier is proposed as seen in Figure 1 and implemented using the CADENCE Virtuoso in 180 nm Technology.

Figure 1: Basic vedic multiplication method

DOI: 10.9790/4200-14030108 www.iosrjournals.org 1 | Page

Vedas, which are ancient Hindu scriptures. This system is known for its unique and efficient techniques for performing mathematical calculations, including multiplication. There are special 16 sutras which describe the vedic Multiplication. Like Ekadhikina Purvena, Nikhilam Navatashcaramam Dashatah, Paraavartya Yojayet. These sutras describe the natural way of solving mathematical problems. Vedic Multiplier complexity is less as compared with any of other type of multiplier such as booth multiplier architecture[2], Array multiplier[3], Walles-tree multiplier[4] etc. Vedic multiplier hardware uses less no of transistors. Therefore Vedic multiplier has more advantages in the terms of on chip area or transistor count, propagation delay [5], power dissipation and complexity. In simple way it gives high performance [6] in compare to others. Using these techniques in the computation algorithms of the co-processor will reduce the complexity, execution time, area, power etc.

We basically worked on the URDHVA- TIRYAGBYHAM which is nothing but multiplication vertically, cross wise and then addition. This technique is shown in figure.1. We have worked on some similar technique but with small changes in it. This works by separating the one 4 bit number into 2 different 2 bit numbers. Then we can multiply the 4 bit number by 2 bit numbers separately ex. A3A2A1A0 is first number and B3B2B1B0 is second number which we have to multiply. Then the Bisget divide into 2 groups like (B3 B2) are MSB bits and (B1 B0) are LSB bits. Modified 4×2 multiplication shown in Figure.2.

Figure 2: Modified 4×2 multiplication method

## II. Design

According to the URDHVA-TIRYAGBYHAM the vedic multiplier is designed below. The  $4\times2$  vedic multiplier block and with help of this block the  $4\times4$  vedic multiplier is designed.

#### Design Of 4×2 Vedic Multiplier

As per shown in Figure.2, the  $4\times2$  vedic multiplier is designed. The output equations of  $4\times2$  Vedic Multiplier is

Y0=A0.B0

Y1 = A1.B0 + A0.B1

Y2=A2.B0+A1.B1+C0 Y3=A3.B0+A2.B1+C1 Y4= A3.B1 + C2 Y5=C3

The Modified 4×2 Vedic multiplier is shown in the Figure.3 below

Figure 3: Modified 4×2 VEDIC Multiplier Block Diagram

#### Design of 4×4 Vedic Multiplier

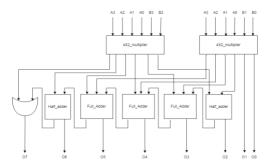

Using the designed module of  $4\times2$  vedic multiplier the  $4\times4$  vedic multiplier is designed as shown in Figure 4. In Design of  $4\times4$  vedic multiplier 2 blocks  $4\times2$  multiplier is used along with half adder [7], full adder [8] AND OR gate circuits for the addition of bits.

Figure 4: Modified  $4\times4$  VEDIC Multiplier Block diagram

# III. Experimental

The schematic and simulation results of the standard blocks along with Proposed design's is given below figures. For the design of 4×2 vedic multiplier AND gate, OR gate, HALF ADDER and FULL ADDER is used. To design the 4×4vedic multiplier the OR gate along with above mentioned circuits is used.

#### **AND Gate**

We designed the AND gate by CMOS approach, it have less power dissipation and less delay along with good voltage levels. The results of the simulation is given below in Figure.5.

Figure 5: Conventional AND gate diagram

#### **OR** Gate

We designed the OR gate by CMOS approach, it have less power dissipation and less delay along with good voltage levels. The results of the simulation is given below in fig- ure.6.

Figure 6: Conventional OR gate diagram

## **Half Adder**

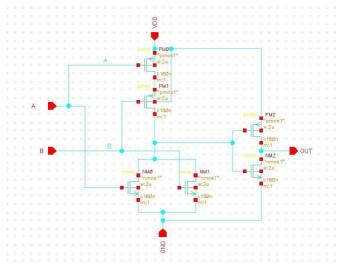

Half adder is a basic digital circuit which performs the addition of two binary bits. It is one of the most important circuit in Arithmetic addition of binary numbers. There are lots of ways to design the Half adder circuit. Like us- ing EXOR gate and AND gate[?], using pass transmission logic etc. We have designed the Half Adder using 10 transistor with Hybrid logic. The schematic and the results of the 10T half adder circuit is given below in Figure. 7.

Figure 7:10T modified half adder diagram

The results of Half adder is verified on the frequency of 500MHz. The circuit gives the output as sum and carry. The result of the above represented 10T half adder circuit is shown in Figure. 8

Figure 8: 10T modified half adder Result

## Full Adder

The full adder circuit is basic digital circuit which is used for the addition of the three one bit binary number and generate the result in form of the sum and carry. Similar as the half adder, full adder

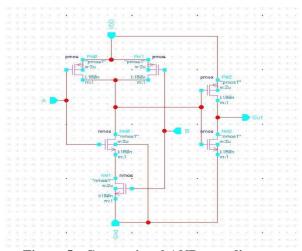

[9] can be designed using many different approaches. Basic full adder can be designed using the 2 half adder and 1 OR gate circuits. We have designed the Full adder using the 20T modified full adder design approach. The 20T full adder is shown in schematic diagram given in Figure.9.

Figure 9:20T modified full adder diagram

The results of Full adder are verified on the frequency of  $500\,$  MHz. The results shown in Figure  $.10\,$  below

Figure 10:20T modified full adder Result

## 4×2 Vedic Multiplier

The  $4\times2$  vedic multiplier is designed using all the blocks above mention such as Half adder, Full adder, OR gate and AND gate. The schematic diagram of the  $4\times2$  vedic multiplier is shown in below Figure.11

Figure 11: Modified 4×2 multiplier schematic

Figure 12: Modified 4×2 multiplier Result

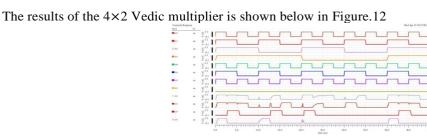

## **4×4 Vedic Multiplier**

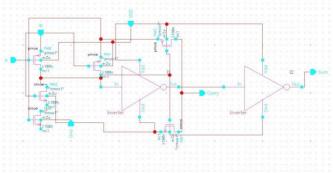

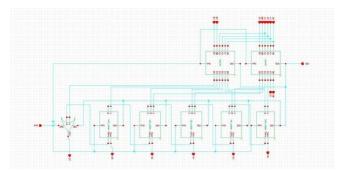

Our final objective is to design  $4\times4$  vedic multiplier [10]. We used the basic block of half adder, full adder and  $4\times2$  vedic multiplier to design it. The schematic of this blockis shown below in Figure. 13

Figure 13:Modified schematic of 4×4 vedic multiplier

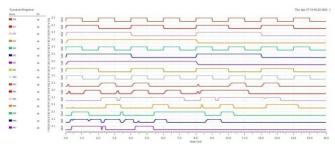

The simulation results of the modified  $4\times4$  vedic multiplier is shown below in Figure.14.The A3A2A1A0 And B3B2B1B0 are the inputs for multiplier [6] while the O0-O7 are the outputs.

Figure 14: Modified 4×4 vedic multiplier result

The result of vedic multiplier is verified at the frequency of 500MHz.

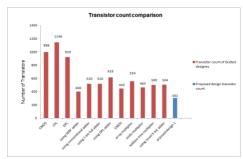

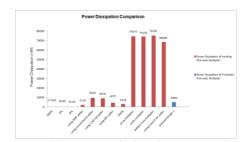

# IV. Result And Comparative Analysis

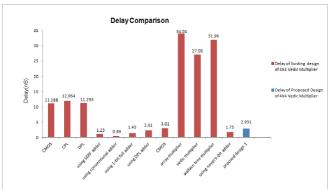

The comparison and analysis of the Vedic multiplier [6] in terms of the Transistor count, Power dissipation and Delays is given below in table.1 and also the graph of the data is shown below in Figure 15-17.

|                   | Table.               | 1                 |          |

|-------------------|----------------------|-------------------|----------|

| Design            | No.of<br>Transistors | Power dissipation | Delay    |

| CMOS              | 998                  | 11.188ns          | 17.034nW |

| CPL               | 1146                 | 12.068ns          | 30.849nW |

| DPL               | 920                  | 11.293ns          | 25.599nW |

| Using SERF        | 400                  | 1.23ns            | 2.11uW   |

| adder             |                      |                   |          |

| Conventional      | 520                  | 0.39ns            | 9.55uW   |

| adder             |                      |                   |          |

| Using 1BIT        | 520                  | 1.45ns            | 9.07uW   |

| adder             |                      |                   |          |

| Using DPL         | 616                  | 2.31ns            | 4.47uW   |

| adder             |                      |                   |          |

| Using TX-         | 445                  | 3.01ns            | 3.11uW   |

| GATE adder        |                      |                   |          |

| Array multiplier  | 554                  | 34.04ns           | 745.7uW  |

| Vedic multiplier  | 464                  | 27.09ns           | 741.3uW  |

| Wallace-tree      | 500                  | 31.96ns           | 752.2uW  |

| multiplier[11]    |                      |                   |          |

| Vedic multiplier  | 464                  | 27.09ns           | 741.3uW  |

| Proposed Modified | 302                  | 2.931ns           | 5.09uW   |

| Vedic Multiplier  |                      |                   |          |

Figure 15: Transistor count comparison

Figure 16: Power dissipation comparison

Figure 17: Delay comparison

# V. Conclusion

The results of proposed design 1 shows the improvement of approx 70% in the number of transistors and 73% less delay but it has high power dissipation in comparison to CMOS Vedic multiplier. All though this circuit have high propagation delay (Tpd) in compare to some other designs shown in table.1.So,the analysis shows that by using the proposed architecture for Vedic multiplier the NO. of transistor required will reduce significantly.

#### **Future Plan**

Future work can include the reduction of the power dissipation and dependency of performance on change in technology trend and implementation of same architecture for higher bit size.

### References

- [1] M. Durga Madhuri, G. Sweta Sree, D. Raghunadh, G. Panduranga Vittal, And Ch. Suryanarayana5. Implementation Of High Speed Vedic Multiplier. International Journal Of Innovative Science And Research Technology, 2, 2017.

- [2] Ahsan Rafiq, Shabbir Majeed Chaudhry, Kamran Sadiq Awan And Muhammad Usman. An Efficient Architecture Of Modified Booth Multiplier Using Hybrid Adder. In 2021 International Bhurban Conference On Applied Sciences And Technologies (Ib- Cast), Pages 648–656, 2021.

- [3] J. Jayakumar. Design Of Low Power Multiplier Using Cadence Tool. International Journal For Technological Research In Engineering, Volume 3, March-2016.

- [4] V. Rajmohan And O. Uma Maheswari. Low Power Modified Wallace Tree Multiplier Using Cadence Tool. World Engineering& Applied Sciences Journal, L 7, 2016.

- [5] Er. Harjinder Singh, Er. Mandeep Sing And Er. Gaurav Mittal . Design Of Low Power Vedic Multiplier By Using 180nm Technology. International Journal Of Innovative Research In Technology, 1:25–31, 2014.

- [6] Hemanshi Chugh And Sonal Singh.Design And Implementation Of A High-Performance 4-Bit Vedic Mul-Tiplier Using A Novel 5-Bit Adder In 90 Nm Technology. In 2022 10th International Conference On Reliability, Infocom Technologies And Optimization (Trends And Future Directions) (Icrito), Pages 1–6, 2022.

- [7] Sunita Dahiya Rituraj Yadav, Ashish Sura. Half Adder Design Using Various Technologies And Comparison Of Various Parameter Performance .International Journal Of Engineering Applied Sciences And Technology, 6, 2021.

- [8] Kavita Khare And Krishna Dayal Shukla. Design A 1bit Low Power Full Adder Using Cadence Tool. Aip Conference Proceedings, 1324(1):373–376, 2010.

- [9] Priyadarshini N.J. A Ptl Based Full Adder Design Using Cadence. International Journal For Research In Applied Science And Engineering Technology, 8.8:141–148.,2020.

- [10] Bs Premananda, Samarth S Pai, B Shashank, And Shashank S Bhat. Design Of Area And Power Efficient Complex Number Multiplier. In Fifth International Conference On Computing, Communications And Networking Technologies (Icccnt), Pages 1–5. Ieee, 2014.

- [11] Y G Praveen Kumar, B S Kariyappa, S M Shashank, And Cn Bharath. Performance Analysis Of Multipliers Using Modified Gate Diffused Input Technology. Iete Journal Of Research, 68(5):3887–3899, 2022.