# Implementation of Fault Tolerant Parallel Filters Using ECC Technique

Ramya Nallagopula<sup>1</sup>, Murthy Raju Kommisetty<sup>2</sup>

<sup>1</sup>M.Tech-VLSID, Department Of ECE, Shri Vishnu Engineering College for Women (Autonomous), Bhimavaram, India <sup>2</sup>Associate Professor, Department Of ECE, Shri Vishnu Engineering College for Women (Autonomous), Bhimavaram, India

**Abstract:** In this paper, using hamming code technique the parallel FIR filters is designed and implemented. In DSP systems the digital filters are very important and in present days the complex circuits are designed and reliability is an important criteria. Fault tolerant parallel FIR filters are to be implemented for reliability purposes. Using case study the improvements in error correction and circuit cost is determined. By using this hamming code technique, the FIR filter is considered as a bit. By using more filters the area is increased and the delay is reduced to improve performance of the circuit. **Key Words:** Faults, Parallel FIR filters, Hamming codes

## I. Introduction

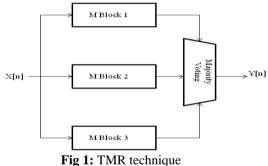

In present days, the Nano technology is using many applications & their reliability is becoming very difficult to face these challenges like faults the fault tolerant parallel filters are used to add redundancy. The simple technique used is Triple Modular Redundancy(TMR) technique and the block diagram for TMR is shown in figure 1,

In this technique, the inputs are given to three similar 'M' blocks and by using majority voting the errors are corrected.TMR is simple to design but the demerits of this technique is the area & power is increased and it does not suits for large number of filters. By using Hamming code technique the single errors can be corrected and by increasing parallel filters the FIR filter the performance of the circuit increases. By using one redundant module, the single fault correction is done. In section 2 the FIR filter design & in section 3 parallel filters with same response is discussed and in section 4 the proposed system and case study is implemented and in section 5 the synthesis and simulation results & in section 6 conclusion is discussed.

## **II.** Fir Filters

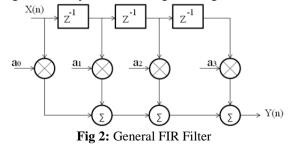

For high performance applications the FIR filter design is used. These filters are easy to design to match a given response and they have good stability. The block diagram for general FIR filter is shown in fig 2.

The FIR filter equation is given as,

$$y[n] = \sum_{i=0}^{N-1} x[n - i].h[i]$$

Where,

x[n] is input signal, y[n] is output signal and h[i] is impulse response.

#### **III. Parallel Filters With Same Response**

1)

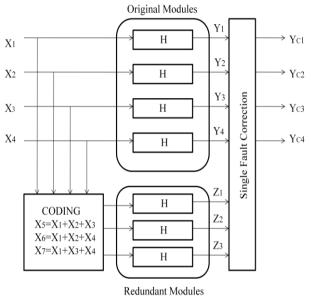

Consider a set of 'K'parallel filters with same response and different input signals. The block diagram for parallel filters is shown in figure 3.

By using Hamming codes the protection of parallel FIR filters is done and Hamming codes are used to correct single errors and it can detect double bit errors. The Rule for finding parity bits using Hamming codes is given as,

$$2^{P} \ge x + p + 1$$

Where, X denotes number of data bits & P denotes number of parity bits.

#### **IV. Proposed Method**

Consider parallel FIR filter using hamming code with message bits '4' and total bits as '7' to obtain parity bits as '3'. The parity bits are calculated by using the data bits and the parity bit equations are calculated as,

p1=d1 xor d2 xor d3 p2=d1 xor d2 xor d4 p3=d1 xor d3 xor d4

.....(3)

...(2)

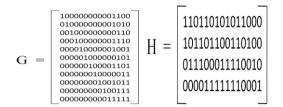

By using the actual input data, the error bits present in any of the bit are stored & replaced with that data. To find the parity bit errors the outputs are compared with the stored results. By using the generating 'G' matrix and parity check 'H' matrix the Hamming Code is represented as,

| G = | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\mathbf{H} = \begin{vmatrix} 1 & 1 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 1 & 0 & 1 \\ 1 & 1 & 0 & 1 & 0 & 1 \end{vmatrix}$ | ) 1 0 |

|-----|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|

|     | 0010101                                              | 101100                                                                                                               | ) 1   |

From above example,

The error in d1 results the errors on p1,p2,p3 check bits and the error in d2 results errors on p1 and p2 and an error in d3 results on p1 and p3 and finally error in d4 results on p2 and p3. The error bit position is shown in table 1 as,

| S1 S2 S3 | Error Bit Position | Action     |  |

|----------|--------------------|------------|--|

| 000      | No Error           | None       |  |

| 111      | d1                 | Correct d1 |  |

| 110      | d2                 | Correct d2 |  |

| 101      | d3                 | Correct d3 |  |

| 011      | d4                 | Correct d4 |  |

| 100      | p1                 | Correct p1 |  |

| 010      | p2                 | Correct p2 |  |

| 001      | р3                 | Correct p3 |  |

Fig 4: Error Location In Hamming Code

The block diagram for 4 parallel FIR filters & hamming code is given in figure 4,

Fig 5:Hamming code technique For 4 Filters

The Encoding is calculated as,

$y = x \cdot G$  .....(4) For identifying the position of the error bit i.e., syndrome is calculated as,

$$S = y \bullet H^{1}$$

т

$S = y \circ H$ Where '•' denotes XOR and multiplication operation. After finding the eerror bit, the error bit is inverted to get the final correct output.

The check filters Zj is calculted as,

$$Z_{1}[n] = \sum_{l=0}^{\infty} (X_{1}[n-l] + X_{2}[n-l] + X_{3}[n-l]) \cdot h[l]$$

$$Z_{2}[n] = \sum_{l=0}^{\infty} (X_{1}[n-l] + X_{2}[n-l] + X_{4}[n-l]) \cdot h[l]$$

$$Z_{3}[n] = \sum_{l=0}^{\infty} (X_{1}[n-l] + X_{3}[n-l] + X_{4}[n-l]) \cdot h[l]$$

.....(6)

Checking is done by,

$\begin{array}{l} Z1[n] = Y1[n] + Y2[n] + Y3[n] \\ Z2[n] = Y1[n] + Y2[n] + Y4[n] \\ Z3[n] = Y1[n] + Y3[n] + Y4[n] \end{array}$

DOI: 10.9790/4200-0604021925

If an error on Y1 is detected then the error is corrected by,  $Yc1[n] = Z1[n] - Z2[n] - Z3[n] \dots(7)$

The ECC technique can be used for more number of parallel filters to provide effectiveness in error correction and to improve performance.

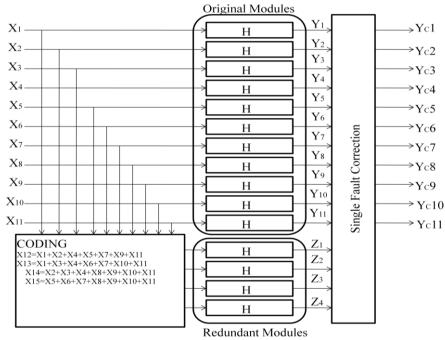

Consider a block of eleven parallel filters for hamming code with k=11 and n=15 is implemented. Mainly the proposed scheme is based on four factors. Theyare Encoding, syndrome calculation, Error analysis and single fault correction. For eleven parallel filters only four redundant modules are used. The reliability is more for 11 parallel filters than 4 parallel filters. The reductions for eleven parallel filters are large only where the number of filters are increased. By using ECC's as the area increases, the delay decreases. Consider an example with generating matrix 'G' and Parity 'H' matrix is,

The block diagram for eleven parallel filters is shown in figure 5.

Fig 6:Hamming code technique For 11 Filters

The area is increased by using the eleven parallel filters and the time period is reduced to improve the performance when more number of filters used in design. Finally, the effectiveness in error detection and correction is evaluated by using the case study. Consider a set of parallel FIR filters with the input data and coefficients. Two evaluations are implemented for a block of parallel filters with data bits k=4 & k=11 and total bits n=7 & n=15 bits. These techniques are synthesized and simulated by using a tool Xilinx Spartan 3E. The fault injection experiments and effectiveness in terms of error correction is done by using eleven parallel filters. For input filters and the coefficients the errors are injected randomly and in all these cases the single errors can be injected in various simulations can be detected and corrected. So, by using case study the effectiveness is confirmed to correct the single errors and system cost is determined.

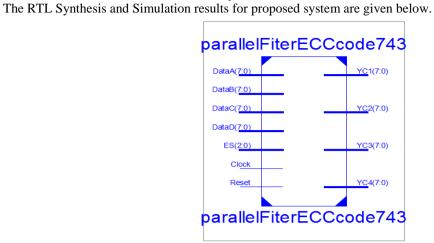

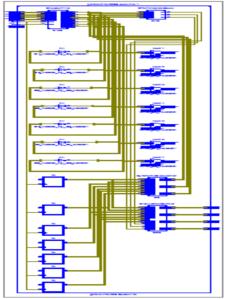

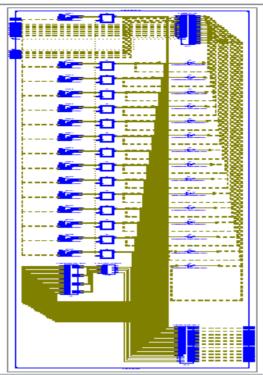

V. Synthesis & Simulation Results

# Fig 7: RTL Schematic for 4 Parallel Filters

Fig 8: Internal Diagram for 4 Parallel Filters

Fig 9: RTL Schematic for Eleven Parallel Filters

Fig 10: Internal Diagram for 11 Parallel Filters

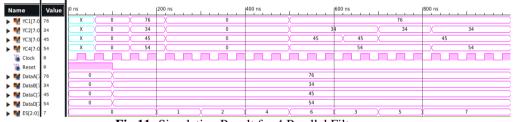

Fig 11: Simulation Result for 4 Parallel Filters

|               |    | ·····   |       |          |          |          |           |        |       |        |    |

|---------------|----|---------|-------|----------|----------|----------|-----------|--------|-------|--------|----|

| NC1[7:0       |    | X 0 44  | × •   | X 44 X 0 | X 44     | XO       | X         | 44     | X     | 44     |    |

| ACSI2:0       |    | x 0 34  |       | X 34 X 0 | X 34     | X o      | X 34 X 34 | X 35 X |       | 34     |    |

| YC3[7:0       | •  | X 0 33  | X o   | 33 0     | 33 33    | 33 0     | X         |        | 33    |        |    |

| YC4[7:0       | •  | X 0 46  | X o   | X 46 X 0 | X 46     | XO       | X         | 46     | 46    | X 46   |    |

| YC5[7:0       | •  | X 0 47  |       | X 47 X 0 | 47       | XO       | X 47 X    |        | 47    |        |    |

| TC6[7:0       | •  | X 0 67  |       | C 67 C 0 | X 67 X 6 | 7 X O    |           |        | 67    |        |    |

| TC7[7:0       | •  | X 0 77  |       | X 77 X 0 | 77       | Xo       | X         | 77     |       | 77     |    |

| YC8[7:0       | •  | X 0 67  | X °   | 67 0     | 67       | XO       | X         |        | 67    |        |    |

| YC9[7:0       | •  | X 0 89  | X o   | X 89 X 0 | X 89     | X 0      | X 89      | 88     |       | 89     |    |

| ► TH YC10[7:  | •  | X 0 77  | X o   | X 77 X 0 | X 77     | X 77 X 0 | X         |        | 77    |        |    |

| TYCI1[7]      | •  | × 0 34  | X o   | 34 0     | 34       | XO       |           |        |       | 34     |    |

| Clock         | 1  | JULU    | JULIU | uuuu     | tinn     | unuu     | JULIU     | uuu    | unuu  | المحمد | பா |

| Reset         | 0  |         |       |          |          |          |           |        |       |        |    |

| > THE DataAll | 44 | • X     |       |          |          |          | 64        |        |       |        |    |

| DataB         | 34 | 0       |       |          |          |          | 84        |        |       |        |    |

| DeteC[]       | 33 | _ O     |       |          |          |          | 33        |        |       |        |    |

| ► THE DataDI  | 46 | • X     |       |          |          |          | \$6       |        |       |        |    |

| DataE[]       | 47 | • X     |       |          |          |          | 47        |        |       |        |    |

| DataF17       |    | 0       |       |          |          |          | 57        |        |       |        |    |

| DataGE        |    | • X     |       |          |          |          | 77        |        |       |        |    |

| DataH         |    | 0 X     |       |          |          |          | 57        |        |       |        |    |

| Datail7       |    | - · · · |       |          |          |          | 39        |        |       |        |    |

|               | 77 | • X     |       |          |          |          | 77        |        |       |        |    |

| DataKD        |    | 0 X     |       |          |          |          | 34        |        |       |        |    |

| ES[3:0]       |    | 0       | 1 2   | 3 4      | 5 6      | 7 8      | 9 10      | 11 12  | 13 14 | 15     |    |

| e colorol     | -  |         |       |          |          |          |           | 1      |       |        |    |

Fig 12: Simulation Result for 11 Parallel Filters

# Performance Analysis:

| Design                         | Area<br>(No.of Flipflop's) | Delay      | Frequency   |  |  |

|--------------------------------|----------------------------|------------|-------------|--|--|

| Hamming code<br>for 4 filters  | 112                        | 15.43 nsec | 493.390 MHz |  |  |

| Hamming code<br>for 11 filters | 240                        | 9.172nsec  | 485.909MHz  |  |  |

## **VI.** Conclusion

By using the proposed scheme the protection of parallel FIR filter can be done in DSP systems. The error detection and correction is done by applying ECC's to parallel filter outputs. The effectiveness i.e., circuit overheads and single fault correction is discussed by using case study.

The future scope is the scheme is also done for IIR filters instead of FIR filters. Another extension is instead of using hamming codes another error correction codes can be used.

#### References

- S.Ranjani, Multi fault detection and correction using error correction codes and parsevel checks, IEEE trans.VLSI systems vol .5(4), march 2016.

- [2]. Arun.k.Somani, Soft Error Mitigation Schemes For High Performance & Aggressive Designs, 344 publications, 10 march 2016.

- [3]. T.Saranya, Highly reliable parallel filter design based on reduced precision error correction codes, IEEE trans. VLSI syst.,vol.5(1),ver 3, feb 2015,45-48.

- [4]. R.Mamatha Rani, Design of low power efficient FIR digital filter, IEEE trans. VLSI syst., vol 4(10), October 2014.

- [5]. Dhiraj.k.pradhan, Fault tolerant single error correction encoders, IEEE transactions, springer, 30 march 2011.

- [6]. L.Jessy, Design and analysis of algorithm based error detect-corrections of parallel FFT, vol5(3), March 2016, 134-138.

- [7]. P.Jeevitha, Application of error correction code for pipelined filter with efficient addition structure, IJSETR,vol 3(11), Nov 2014.

- [8]. P.Sneha, FPGA implementation of RPR protected parallel FIR filters, IEEE trans.,vol 10(3), June 2015,57-64.